CrossLinkは、4レーン最大6GbpsのMIPI D-PHYトランシーバ2系統と、15ペアのソースシンクロナスIOを搭載したMIPIインタフェース用のBridge ICです。画像技研では、CrossLinkを使用したBridge FPGAの設計を行っています。

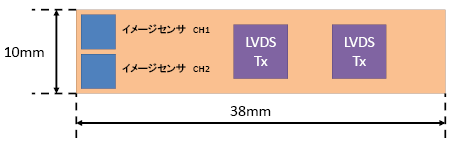

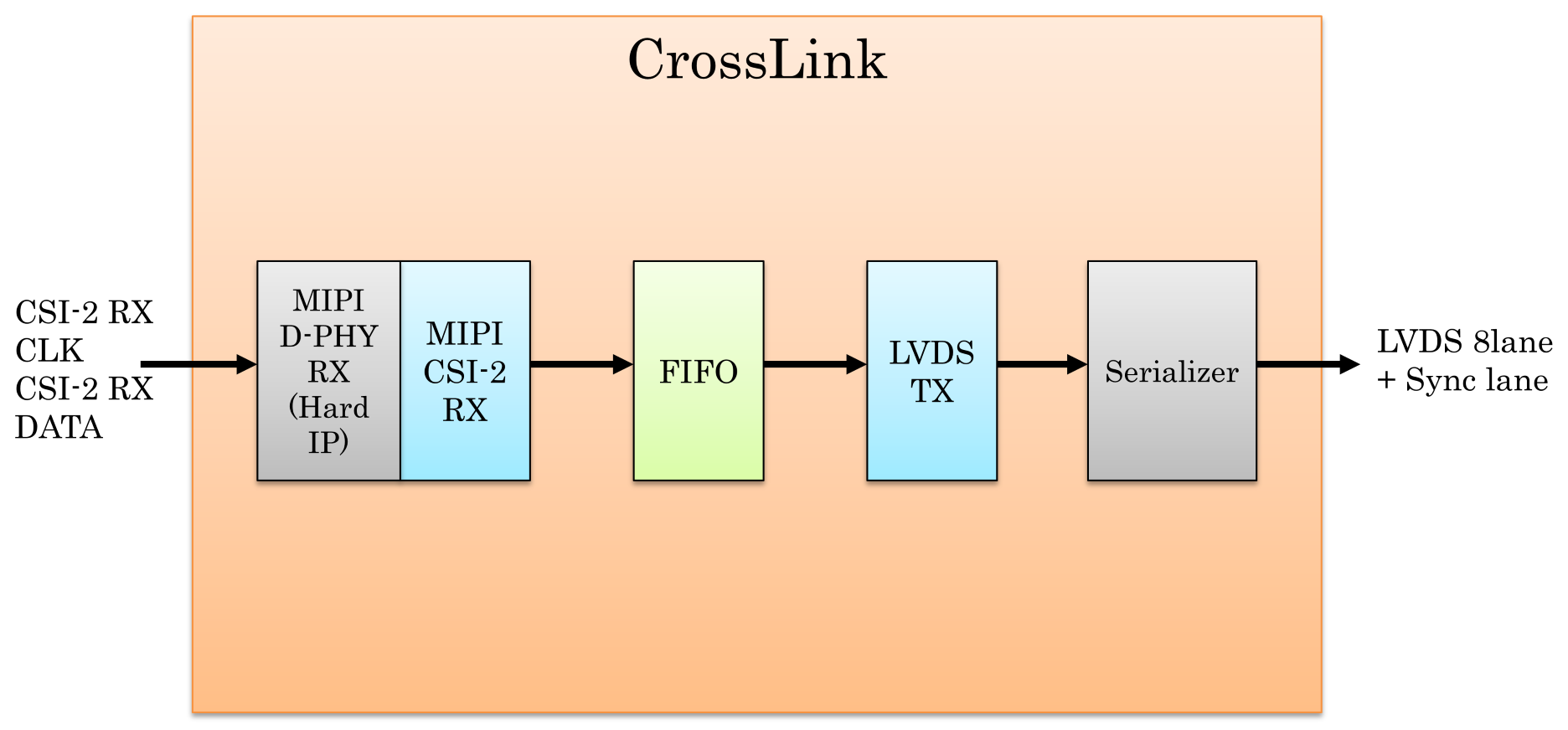

- MIPI to LVDS変換

MIPIのセンサをFPGAやASICに入力するために、LVDSに変換します。

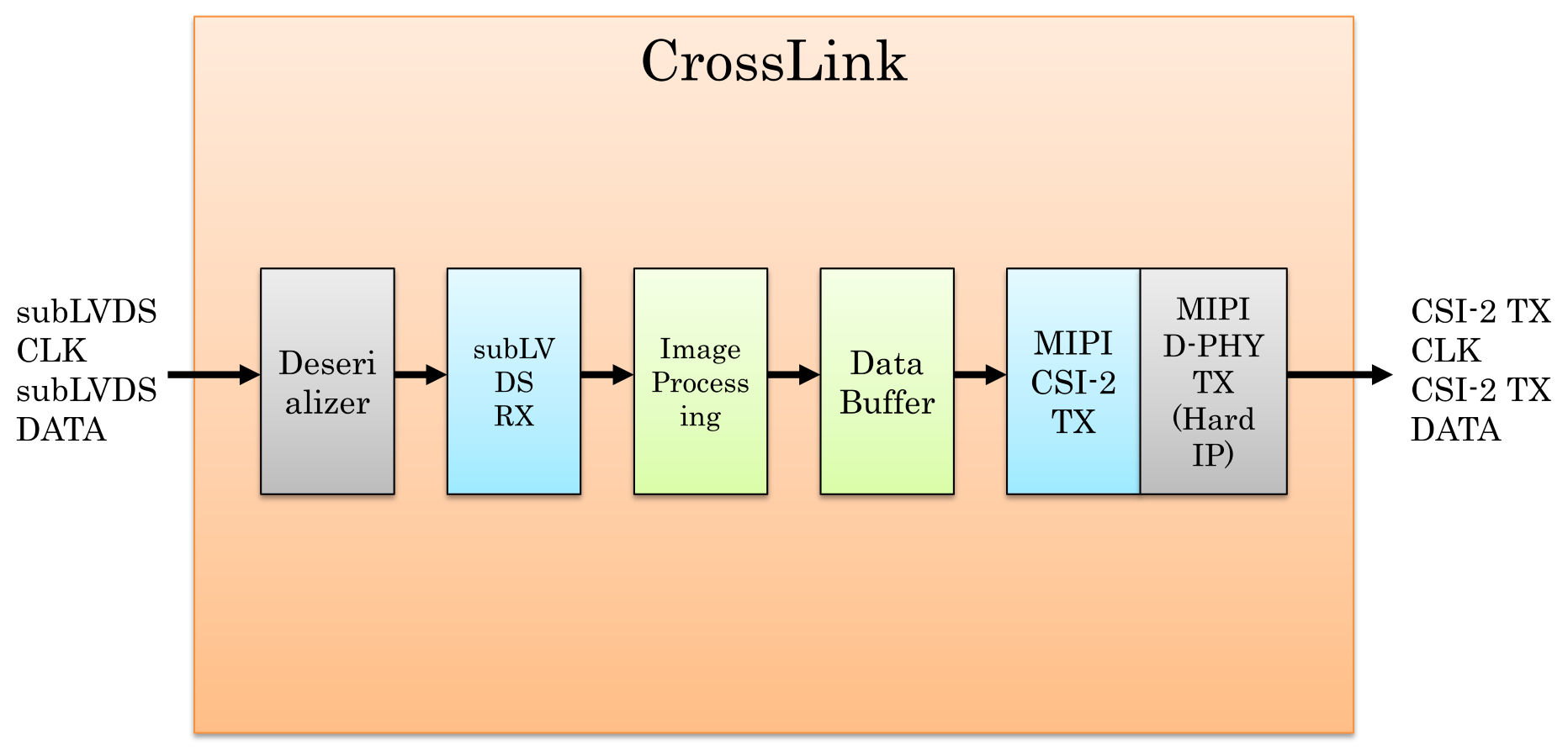

- subLVDS to MIPI変換

subLVDSのセンサをMIPI入力のASSPに入力するために、インタフェース変換を行います。

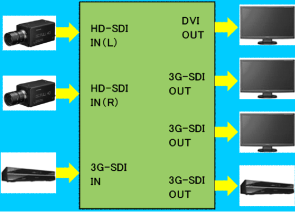

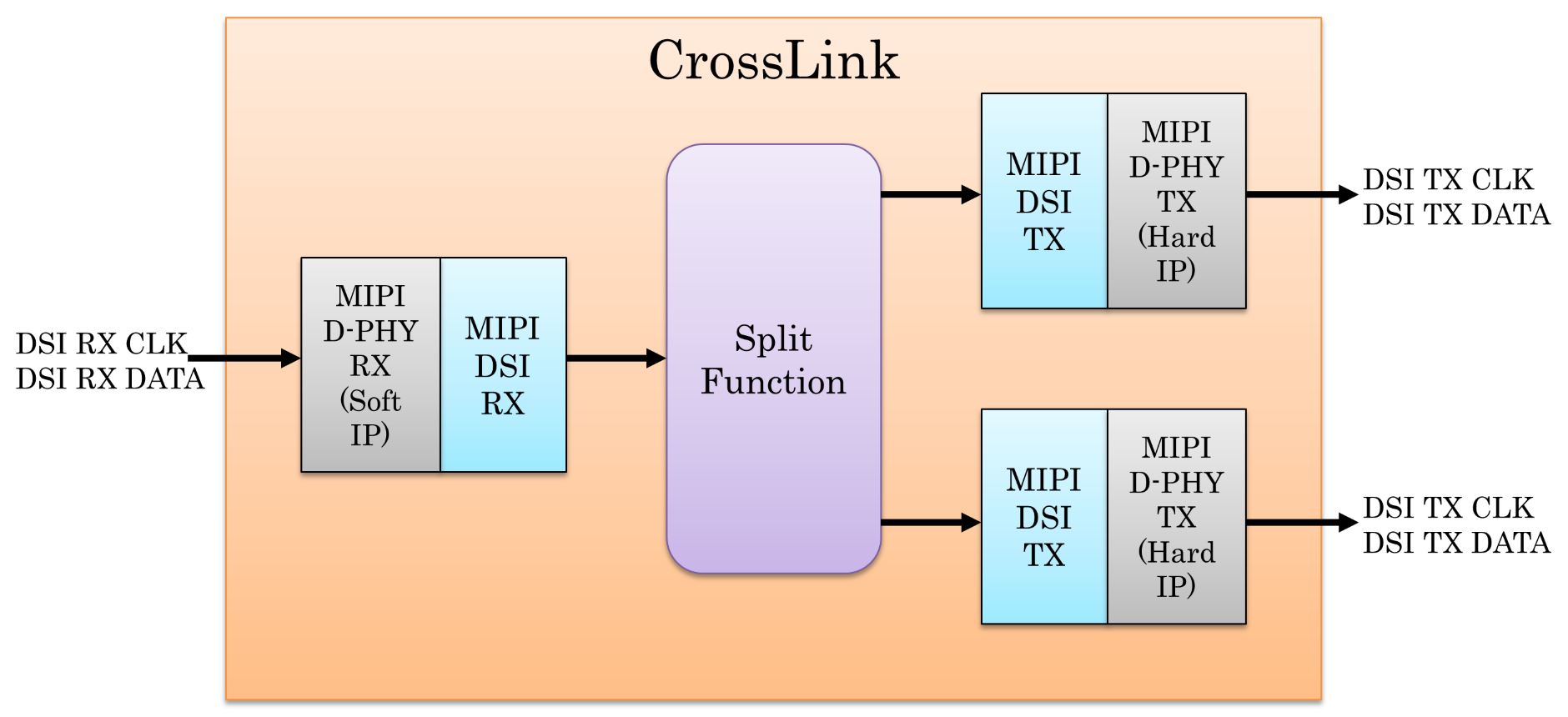

- DSI Splitter

1系統のMIPI DSI入力を2系統に分配します。3D表示で使用します。

このほか、様々なインタフェース変換に対応しています。